隨著晶體管先進(jìn)工藝節(jié)點(diǎn)持續(xù)推進(jìn),國(guó)際半導(dǎo)體產(chǎn)業(yè)界已明確2 nm以后晶體管技術(shù)將轉(zhuǎn)向納米片晶體管技術(shù),包括多橋通道晶體管(Multi-Bridge Channel FET)和垂直互補(bǔ)晶體管(Complementary FET),來(lái)更好地提升靜電控制能力。然而基于傳統(tǒng)硅鍺材料的多橋溝道制造工藝依賴橫向選擇性刻蝕和重復(fù)外延生長(zhǎng),制造工藝日益復(fù)雜。此外,體硅材料制作溝道在厚度小于3 nm時(shí),由于界面缺陷的存在遷移率會(huì)大幅退化,所以硅基多橋溝道結(jié)構(gòu)也仍然面臨漏電流的問題。

所以,半導(dǎo)體業(yè)界亟需一種既能原子尺度薄又能保持良好載流子傳輸能力的新溝道材料,而具有半導(dǎo)體性質(zhì)的二維原子晶體(二維半導(dǎo)體)的出現(xiàn)提供了解決這些問題的可能選擇。因?yàn)槎S半導(dǎo)體具有天然的原子級(jí)厚度的納米片結(jié)構(gòu),和碳納米管、石墨烯一樣,具有光滑無(wú)懸掛鍵的表面,可以很好的延續(xù)摩爾定律的晶體管微縮趨勢(shì);而且二維材料種類豐富、能夠任意堆疊的特點(diǎn),可以用于靈活的器件結(jié)構(gòu)和能帶設(shè)計(jì)。所以,TSMC、Intel、IMEC等領(lǐng)先的半導(dǎo)體公司近年來(lái)正在積極引入二維材料,作為未來(lái)1 nm以下節(jié)點(diǎn)的重要技術(shù)儲(chǔ)備。

鑒于此,復(fù)旦大學(xué)微電子學(xué)院和北京大學(xué)物理學(xué)院的課題組緊密合作,基于晶圓級(jí)二維半導(dǎo)體薄膜,成功制備了MBC-FET和C-FET原型器件陣列。首先,使用晶圓級(jí)的N型MoS2薄膜作為溝道,并通過轉(zhuǎn)移疊層和層間互連工藝實(shí)現(xiàn)兩層的MBC-FET器件;其次通過在基底上直接生長(zhǎng)的P型MoTe2薄膜,通過疊層轉(zhuǎn)移N型MoS2和層間互連,實(shí)現(xiàn)垂直C-FET器件。該成果為二維半導(dǎo)體材料在未來(lái)MBC-FET和C-FET先進(jìn)工藝節(jié)點(diǎn)中的實(shí)際應(yīng)用提供了規(guī)?;圃斓尿?yàn)證下結(jié)果。夏銀、宗凌逸、潘宇為共同第一作者,復(fù)旦大學(xué)包文中研究員和周鵬教授、北京大學(xué)葉堉教授為共同通訊作者。該工作同時(shí)還與華東理工大學(xué),深圳六碳科技等單位緊密合作,并得到了科技部重點(diǎn)研發(fā)計(jì)劃納米科技專項(xiàng)、上海市科委集成電路科技支撐專項(xiàng)等項(xiàng)目的支持。

此工作中的MBC-FET是由兩層平行的被環(huán)形柵電極包裹的MoS2溝道構(gòu)成,兩層MoS2的對(duì)應(yīng)源漏電極通過互聯(lián)工藝相連。圖1所示為MoS2的MBC-FET 立體和橫截面結(jié)構(gòu)示意圖、陣列圖片,以及器件截面的TEM表征。

圖1. (a) 基于MoS2的MBC-FET三維結(jié)構(gòu)示意圖;(b) MBC-FET器件陣列的光學(xué)圖;(c) 基于MoS2的MBC-FET的截面示意圖;(d)MBC-FET的截面高清TEM表征,左上角的內(nèi)嵌圖是三層MoS2的AFM,右上角的內(nèi)嵌圖是三層MoS2截面的高清TEM表征。

其次,圖2 (a)-(c)展示了單柵、雙柵以及MBC結(jié)構(gòu)柵控的晶體管的轉(zhuǎn)移特性性能對(duì)比。在VDS 為1 V 和 2 V的條件下,同樣面積尺寸的單柵和雙柵晶體管的驅(qū)動(dòng)電流分別為0.6 μA and 3.2 μA,而MBC-FET的驅(qū)動(dòng)電流增加到了45 μA。并且其關(guān)態(tài)電流僅為10-13 A。圖(g)給出了單柵、雙柵以及MBC-FET的電學(xué)性能對(duì)比,分別各統(tǒng)計(jì)了15個(gè)器件的電學(xué)性能。整體來(lái)看,相比于單柵和雙柵晶體管的性能,二維半導(dǎo)體作為溝道的MBC-FET的性能得到了極大的提高,具有更大的驅(qū)動(dòng)電流,更高的遷移率以及更小的亞閾值擺幅(SS),并且開關(guān)比仍然可以保持。

圖2. (a)-(d), (b)-(e), (c)-(f) 單柵FET,雙柵FET以及MBC-FET的轉(zhuǎn)移特性和輸出特性性能對(duì)比;(g) 單柵FET,雙柵FET以及MBC-FET的電學(xué)性能對(duì)比。

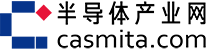

然后,作者們通過對(duì)上下兩層的MoS2溝道通過不同的層間互連,實(shí)現(xiàn)了多種數(shù)字邏輯。如圖3(a-b) 所示,將上層MoS2 晶體管的柵源電極短接作為負(fù)載管,并將上層晶體管的源極與下層晶體管的漏極相連,再將中間的柵電極接地,從而屏蔽了頂部和底部柵極對(duì)另一側(cè)溝道的影響。該垂直反相器的測(cè)試結(jié)果如圖3(c)所示,VDD從1V增加到3V,反相器的增益從1.8增加到6.8。基于垂直的兩層MoS2溝道,作者同時(shí)也制備了NAND和NOR邏輯。該垂直結(jié)構(gòu)相較于傳統(tǒng)的平面結(jié)構(gòu)可以省下2/3的電路面積。該結(jié)構(gòu)的NAND和NOR的動(dòng)態(tài)響應(yīng),如圖(e)和(g)所示。

圖3. (a)-(b) 基于n-MoS2 FET的垂直反相器的光學(xué)圖和電路結(jié)構(gòu)示意圖;(c) 垂直反相器的電壓轉(zhuǎn)移特性和電壓增益曲線;(d)-(f) NAND和NOR的電路結(jié)構(gòu)示意圖;(e)-(g) NAND和NOR分別在1Hz的頻率下的動(dòng)態(tài)響應(yīng)。

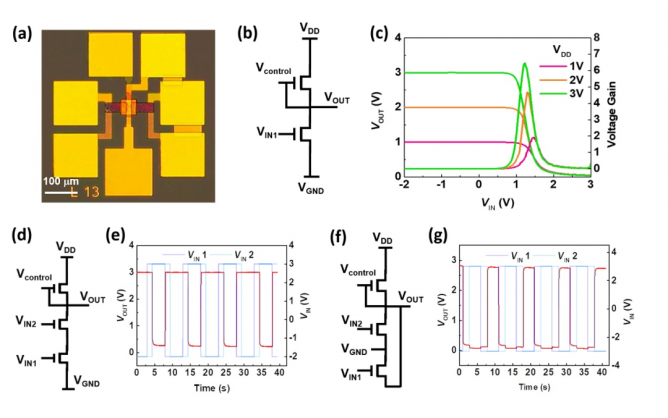

論文的第二部中,作者利用兩種二維半導(dǎo)體材料實(shí)現(xiàn)了垂直C-FET結(jié)構(gòu),其三維示意圖如圖4所示。上層的N型MoS2 晶體管作為反相器的下拉管,下層的P型MoTe2 晶體管作為反相器的上拉管。下拉管的漏極和上拉管的源極通過通孔連接作為VOUT。此時(shí),垂直結(jié)構(gòu)中間的公共柵電極作為VIN,下拉管的源極接地,上拉管的漏極接VDD。此時(shí),MoTe2溝道和MoS2溝道能夠同時(shí)被中間的公共柵電極調(diào)控。

圖 4. (a) C-FET的三維結(jié)構(gòu)示意圖;(b)-(c) C-FET陣列的光學(xué)圖;(d) C-FET截面示意圖;(e)-(f) 分別是C-FET溝道區(qū)域和VDD區(qū)域的截面的高清TEM圖。

獨(dú)立測(cè)試的MoTe2 晶體管和MoS2 晶體管的電學(xué)特性如圖(a)-(d)所示,兩種晶體管均展現(xiàn)了良好p型特性和n型特性。接下來(lái)就是C-FET結(jié)構(gòu)的反相器測(cè)試,當(dāng)給中間的公共柵電極施加負(fù)電壓的時(shí)候,MoS2 溝道被關(guān)斷,MoTe2溝道被開啟,VOUT輸出高電平;當(dāng)公共柵電極施加正電壓,MoS2溝道被開啟,MoTe2溝道被關(guān)斷,VOUT輸出低電平。圖3(e) 展示了在偏壓1V到4V下,此C-FET器件的電壓轉(zhuǎn)移特性和電壓增益。在VDD為4V時(shí),C-FET可以獲得7V/V的較好電壓增益。最后,作者還證明了C-FET的閾值開關(guān)電壓可以由不同波長(zhǎng)的光信號(hào)來(lái)調(diào)控,這也證明了C-FET結(jié)構(gòu)在傳感和光電領(lǐng)域的潛在應(yīng)用。

圖5. (a)-(b) MoTe2 FET的轉(zhuǎn)移特性和輸出特性;(c)-(d) MoS2 FET的轉(zhuǎn)移特性和輸出特性;(e) 在偏壓1V到4V下,C-FET的電壓轉(zhuǎn)移特性和電壓增益。

總結(jié):

此工作基于晶圓級(jí)的二維半導(dǎo)體薄膜,成功制備MBC-FET和C-FET結(jié)構(gòu)的晶體管陣列。而且該工作中提出的二維器件工藝與硅基CMOS工藝更為兼容,有利于未來(lái)二維半導(dǎo)體材料的產(chǎn)業(yè)化應(yīng)用。此外,雖然目前陣列器件的最小精度尺寸受限于設(shè)備條件,但是結(jié)合近期學(xué)術(shù)界關(guān)于二維半導(dǎo)體短溝道原型器件的報(bào)道,完全可以驗(yàn)證2 nm節(jié)點(diǎn)中引入二維半導(dǎo)體材料可行性,并進(jìn)一步探究2 nm以下的技術(shù)可行性。

論文信息:

Wafer-Scale Demonstration of MBC-FET and C-FET Arrays based on Two-Dimensional Semiconductors

Yin Xia, Lingyi Zong, Yu Pan, Xinyu Chen, Lihui Zhou, Yiwen Song, Ling Tong, Xiaojiao Guo, Jingyi Ma, Saifei Gou, Zihan Xu, Sheng Dai, David Wei Zhang, Peng Zhou*, Yu Ye*, Wenzhong Bao*

Small

DOI: 10.1002/smll.202107650

原文鏈接:

https://onlinelibrary.wiley.com/doi/10.1002/smll.202107650

原文鏈接:

https://onlinelibrary.wiley.com/doi/10.1002/smll.202107650