近日,電子信息與電氣工程學(xué)院微納電子學(xué)系周健軍教授課題組在IEEE Journal of Solid-State Circuits(JSSC)上發(fā)表題為“A 60MS/s 5MHz-BW Noise-Shaping SAR ADC with Integrated Input Buffer Achieving 84.2dB-SNDR and 97.3dB-SFDR Using Dynamic Level-Shifting and ISI-Error Correction”的模數(shù)轉(zhuǎn)換器(ADC)芯片研究成果。

研究內(nèi)容

該研究重點(diǎn)解決了ADC在系統(tǒng)應(yīng)用中面臨的集成輸入緩沖器時(shí)的設(shè)計(jì)挑戰(zhàn),揭示了ADC符號(hào)間串?dāng)_的產(chǎn)生機(jī)理以及對(duì)ADC精度的影響,文章提出動(dòng)態(tài)電平移位技術(shù)與采樣誤差校正技術(shù),從而實(shí)現(xiàn)了片上集成緩沖器的高性能ADC的線性度提升。

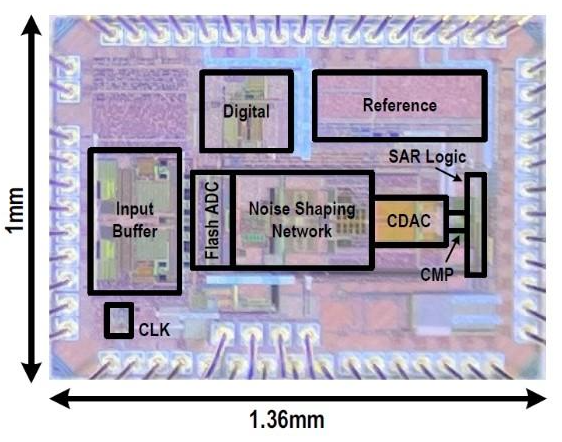

ADC芯片采用CMOS工藝流片驗(yàn)證,在采樣率為60MS/s帶寬為5MHz時(shí),實(shí)現(xiàn)了84.2dB的SNDR和97.3dB的SFDR,達(dá)到了截止論文投稿時(shí)文獻(xiàn)報(bào)道的集成了輸入緩沖器的逐次逼近型ADC的最好優(yōu)值指標(biāo)(FoMw為60.6 fJ/conv.-step,F(xiàn)oMs為172.1dB)。此外,該芯片在設(shè)計(jì)時(shí)采用了多項(xiàng)數(shù)字輔助校準(zhǔn)技術(shù),并考慮了ESD保護(hù)等芯片可靠性問題。

集成輸入緩沖器的逐次逼近型ADC芯片照片

關(guān)于JSSC

IEEE固態(tài)電路期刊(JSSC)是國際集成電路領(lǐng)域最高級(jí)別期刊之一,旨在發(fā)布集成電路設(shè)計(jì)領(lǐng)域的最新技術(shù)進(jìn)展和紀(jì)錄性成果,代表著業(yè)內(nèi)當(dāng)前最高技術(shù)水平。

作者信息

過悅康博士生是論文第一作者,金晶研究員為論文通訊作者。該項(xiàng)研究的參與人員全部來自上海交通大學(xué)微納電子學(xué)系模擬射頻集成電路設(shè)計(jì)中心實(shí)驗(yàn)室。該項(xiàng)研究受到國家自然科學(xué)基金項(xiàng)目資助。

論文鏈接:https://ieeexplore.ieee.org/document/9810848

(來源:上海交通大學(xué))